CEOB2B晶振平台汇集了数千万种晶振产品,只要你需要的,这里都给你准备好了。包括海内外上百种晶振品资料,晶振规格型号,晶振技术解决方案等信息,均可在CEOB2B晶振平台免费获取,有需要人士可收藏网址以便需要时使用。下面给大家讲解到的是石英晶体振荡器中的三态输出技术。

大多数数字系统使用由两个状态级别0和1表示的二进制数系统。在一些特殊应用中,需要第三状态(Hi阻抗输出)。TTL,HCMOS或HCMOS石英晶体振荡器提供三态输出或三态启用/禁用功能。其常见应用包括自动测试,总线布线数据传输。

这三种状态是低,高和高阻抗(HiZ或浮动)。高阻抗状态的输出表现得好像它与电路断开,除了可能有小的漏电流。三态器件具有使能/禁止输入,通常在几乎任何封装的引脚1上。当使能为高电平或悬空时,器件振荡(输出高电平和低电平),当引脚1接地(逻辑“0”)时,器件进入高阻态。

总线是一组通用的电线,通常用于数据传输。三态总线有几个三态输出连接在一起。通过控制电路,除了一个总线上的所有设备都具有高阻抗状态的输出。其余器件使能,驱动高低输出总线。

三态功能的其他应用是用于自动测试设备(ATE)。几个有源晶振,晶体振荡器的输出连接在一起。对于控制电路,除一个振荡器外,所有振荡器都具有高阻抗状态的输出。选择的唯一振荡器将从计数器读出其频率。(图5)

在三态函数生效之前总会有一些延迟。此转换发生在两个转换(禁用和启用时)。从低电平开始的三态输出禁止时间是tPLZ,三态到低电平的输出使能时间是tPZL。(图6)

CMOS

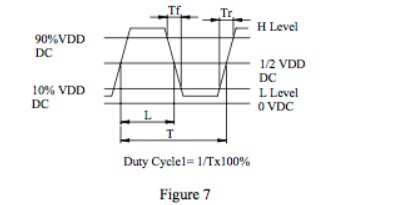

上升和下降时间CMOS技术的上升和下降时间取决于其速度(CMOS,HCMOS,ACMOS,BICMOS),石英晶振的电源电压,负载电容和负载配置。CMOS 40000系列的典型上升和下降时间为30ns,HCMOS为6ns,而ACMOS(HCMOS,TTL兼容)的最大上升和下降时间为3ns。典型的上升和下降时间在其波形水平的10%至90%之间测量。(见图7)

ACMOS输出终止技术

由于ACMOS(HCMOS/TTL兼容)器件的快速转换时间,在测试或测量石英晶体振荡器电气性能特性时必须使用正确的端接技术。端接通常用于解决电压反射问题,这实质上导致时钟波形中的步骤以及过冲和下冲。这可能导致数据的错误时钟,以及更高的EMI和系统噪声。

由于PC板上的迹线长度及其负载配置,还需要端接。有三种终止时钟轨迹的通用方法,即将器件的输出阻抗与线路阻抗相匹配的过程:

方法1:串联终端在串联终端中,阻尼电阻靠近时钟信号源放置。Rs的值必须满足以下要求:Rs≥ZT - Ro

方法2:上拉/下拉电阻在上拉/下拉终端中,组合的戴维宁等效于迹线的特征阻抗。这可能是最干净的,并且不会产生任何反射,也会降低EMI。